若何复习通过大学单片机原理及应用期末测验高分不挂科,有没有相关条记材料和办法?

单片机复习总结

一、概述

1、冯诺伊曼系统

1、接纳二进造暗示数据和指令

2、接纳存储法式的工做体例,即编写法式-存储法式-主动持续地施行法式

3、计算机硬件系统的构成:运算器、存储器、控造器、输入设备和输出设备

2、计算机数值暗示

2进造(B),16进造(H),10进造(D)

带符号数的暗示(原码、反码、补码)

原码 正数 原码 正数

反码 补码

原码取反 负数 反码+1 负数

即已知微型计算机存储的数为负数,则补码减1再取反

八位二进造数、无符号数暗示范畴是0—255,有符号数原码暗示范畴是-127—+127,反码暗示范畴是-127—+127,补码暗示范畴是-128—+127

带符号数溢出:带符号数的补码加、减运算的成果超出了补码暗示的范畴。

判断溢出:两个同符号数相加或者两个异符号数相减时,1)次高位向更高位有进位(借位),而更高位向前无进位(借位);2) 次高位向更高位无进位(借位),而更高位向前有进位(借位)

压缩BCD码:4位二进造数

BCD码

非压缩BCD码:8位二进造数,高四位总为0000

3、串行通信,并行通信的定义

串行通信:数据按位挨次停止传送 低速、远距、廉价、可靠性高、抗干扰性强

并行通信:数据的列位同时停止传送 高速、短距、高贵、可靠性低

二、MCS-51单片机硬件根底

1、硬件构造 领会

1、微处置器(CPU)

2、存储器

3、I/O口

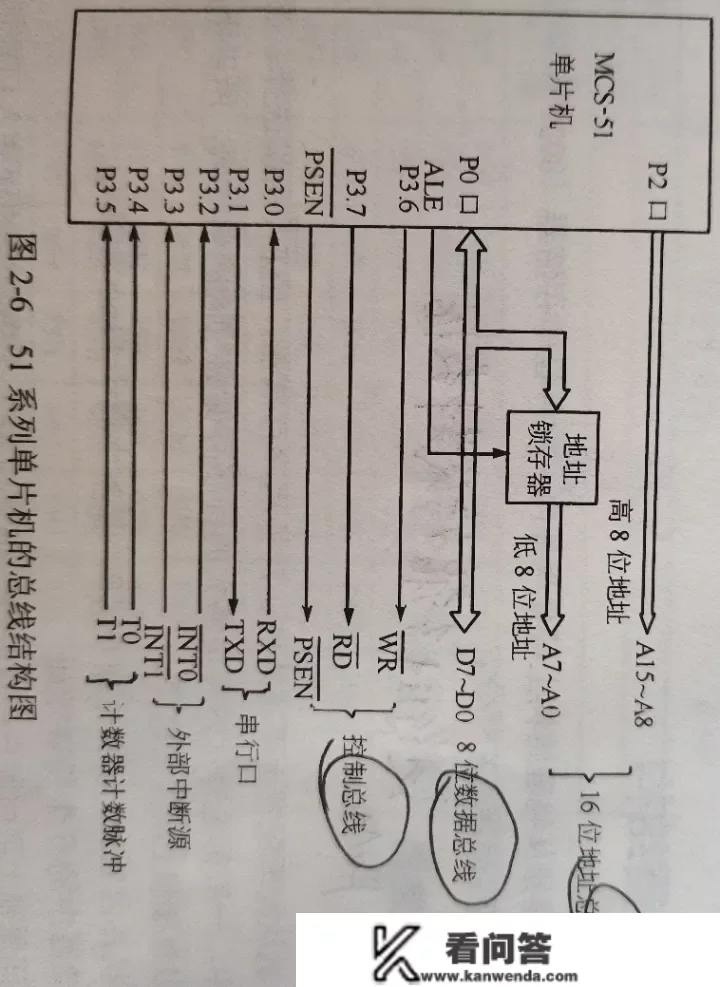

4、外部可拓展16条地址总线,8条数据总线及需要的控造总线

2、引脚功用 熟悉,掌握在外部功用扩展中的应用

1、电源引脚VCC(+5V)、VSS(接地)

2、时钟引脚XTAL1、XTAL2(多接纳内部时钟体例)

3、控造引脚RST(高电平有效)

4、输入输出引脚P0—P3(具有根本的输入/输出功用):

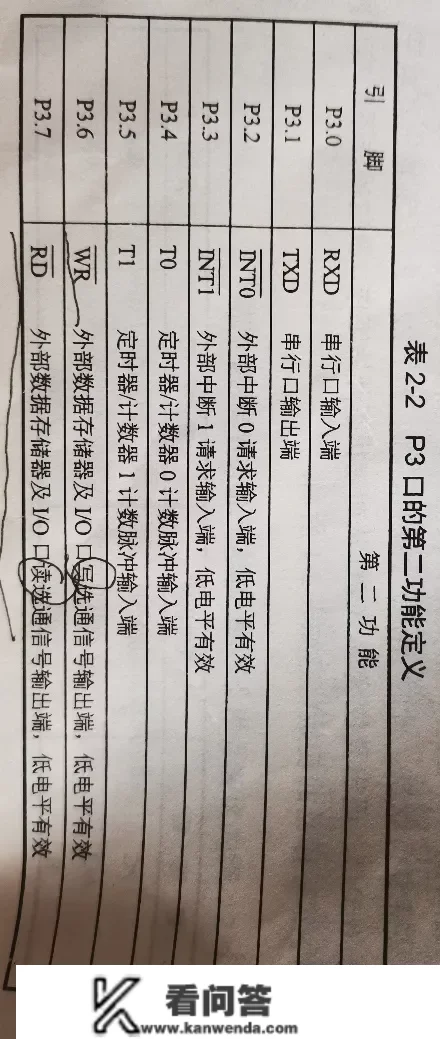

P0、P2、P3具有第二功用:

P0做为低8位地址总线及8位数据总线

P2做为高8位地址总线

5、PSEN(片外法式存储器读选通信号输出端),低电平有效

EA(片外法式存储器选用端),高电平选择片内ROM,低电平选择片外ROM

3、中央处置器 熟悉各个存放器的根本功用

掌握振荡周期、机器周期及指令周期的概念

时钟,复位的定义

振荡周期:为单片机供给按时信号的信号源的周期

形态周期:两个振荡周期

机器周期:6个形态周期

指令周期:施行一条指令所占用的全数时间(乘除为4机器周期,其余为单机器周期和双机器周期)

复位:CPU从初始形态起头工做

4、存储器构造

(1)四个物理空间:内、外法式存储器,内、外数据存储器

三个逻辑空间:法式存储器(ROM),内、外数据存储器(RAM)

(2)法式存储器地址空间(EA引脚选择)

重点掌握:低地址段的保留单位

复位0000H外部中断10013H外部中断00003H按时器/计数器1溢出中断001BH按时器/计数器0溢出中断000BH串行口中断0023H(3)数据存储器地址空间

重点掌握:内部数据存储器,地址范畴,特点,SFR

外部数据存储器,寻址范畴及寻址体例

片内RAM:00H-7FH

片内数据存储器

特殊功用存放器SFR:80H-0FFH

片外数据存储器:0000H-0FFFFH

工做存放器区:临时存放 8 位信息

位寻址区:可用于各类法式形态标记、位控造变量的存入

数据缓冲区:用户 RAM

(4)位处置器

熟悉位处置器构成及位存储器地址范畴

PSW:

PSW.7PSW.6PSW.5PSW.4PSW. *** SW.2PSW.1PSW.0CACF0RS1RS0OV-P1、进位标记C:更高位能否向前一位进位或借位,是则1,不然0

2、辅助进位AC:两个8位数运算,低四位有无进位,有则1,无则0

3、用户自定义标记位

4、工做存放器区选择位RS1、RS0

RS1RS0工做存放器区0000H-07H0108H-0FH1010H-17H1118H-1FH5、溢出标记位0V

加减法:有溢出为1,无溢出为0

乘法:积>255为1

除法:除数为0时为1

6、奇偶标记位P:仅对累加器A操做的指令有影响

累加器A中1的个数为奇数时为1,不然为0

仓库指针SP:8位的公用存放器,用于存放栈顶的位置

数据指针DPTR:16位的公用地址指针存放器,用于存放16位地址,相当于间接存放器

三、指令系统

1、指令的寻址体例(掌握)

7种寻址体例,名称、格局、寻址范畴

1、立即寻址

MOV A,#70H

2、存放器寻址

MOV A,R0

3、间接寻址

MOV A,70H

4、存放器间接寻址(只要R0,R1和DPTR)不克不及拜候SFR,DPTR拜候片外RAM的64KB范畴

MOV A,@R0

5、基存放器加变址存放器间接寻址 常用于拜候法式存储器中的常数表

MOVC A.@A+DPTR 基存放器:A 变址存放器:PC,DPTR

6、相对寻址当出息序计数器PC值加上指令中所给出的偏移量rel

JZ rel

7、位寻址

2、指令系统(五大类)

要求:指令的格局,寻址体例,施行操做,对标记位影响,法式段编写。

1、数据传送类:MOV、MOVC、MOVX、XCH、XCHD、SWAP、PUSH、POP

2、算数运算类:ADD、ADDC、INC、DA A、SUBB、DEC、MUL、DIV

3、逻辑运算类:NAL、ORL、XRL、CLR A、CPL A、RL A、RLC A、RR A、RRC A

4、控造转移类:LJMP、SJMP、JZ/JNZ、CJNE、DJNZ、LCALL、RET、RETI、NOP

5、位操做类:MOV、CLR、CPL、SETB、ANL、ORL、JC/JNC、JB/JNB、JBC

6、伪指令:ORG、DB、DW、EQU、DS、BIT、END

五、P0-P3口的应用根底 课件

1、P0-P3口的特点及功用

1、P0:P0口无上拉电阻接电源,为双向口,施行输出功用时,外部必需接上拉电阻;做为地址线利用时要增加一个锁存器,为低8位,

2、P1:只能做为一般的I/O接口利用

3、P2:高8位地址总线

4、P3:除根本输入输出功用,还有第二功用

2、掌握读引脚体例

利用读引脚指令前,必需先用输出指令置Q=1,使VIT1截行,不然引脚将始末处于低电平上,不成能输入高电平

3、P0-P3口的根本输出以及LED显示(静态显示)的工做原理

查表:

MOV A,#data

MOV DPTR,#DISPTAB

MOVC A,@A+DPTR

4、P0-P3口的根本输入

必需先输出高电平,才气读取该引脚所毗连的外部设备数据

六、中断系统 中断

1、中断的概念

CPU 暂时停下现行法式的施行,转向为临时发作的事务停止处置,处置完后,再返回施行原法式

2、与中断有关的存放器

3、中断源:外部及内部中断源,中断触发体例,若何设置

外部中断:

外部中断0(INT0)

外部中断1(INT1)

电平触发(低电平有效)或沿触发(负跳变有效)

中断恳求信号凹凸电平的形态都应至少维持一个机器周期,以确保电平变革被单片机检测到

内部中断:

1、按时器/计数器

按时器/计数器0(TF0)

按时器/计数器1(TF1)

2、串行口中断

RI

TI

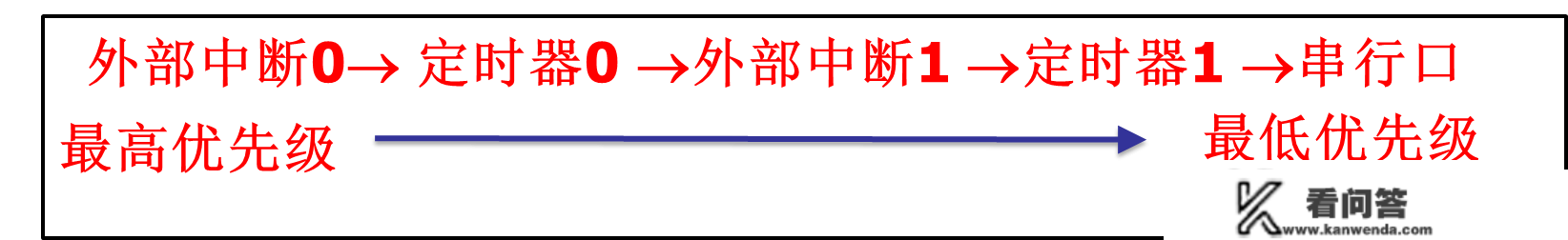

4、MCS-51中断优先级的处置原则,同级中断申请的查询次序

5、中断处置过程(领会),各个中断源对应中断矢量(掌握),中断响应前提(掌握)。

6、中断法式编写的步调

(1)TCON存放器中的IT0、IT1位

IT=1为脉冲触发体例,IT=0为电平触发体例

(2)IP存放器中的PX0、PX1位

(3)IE存放器中的EA、EX0、EX1位(复位后,均清0)

EA为中断允许总控造位,高电平有效

ES为串行口中断

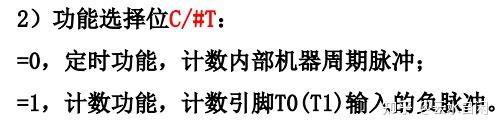

七、按时/ 计数器 按时计数器

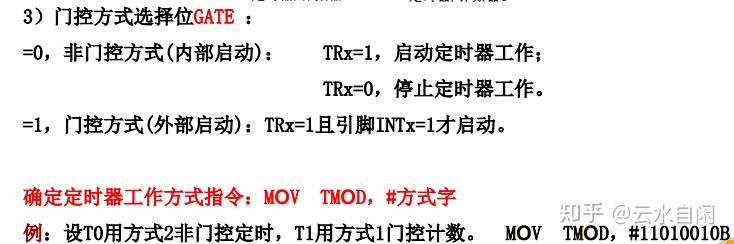

1、初始化法式,中断或非中断情况下的应用编程

2、按时计数器特点:16位加1计数器,计数初值为计数长度的补码;可程控为4种差别工做体例。

3、初始化法式:(1)计数常数的计算

(2)置工做体例字

(3)置THX,TLX

(4)置TRX启动计数

(5)置EA、ETX开中断

4、按时计数器的工做形式及应用编程

输出波形(占空比)

九、并行扩展接口手艺

1、给出接口芯片,画接口电路图,计算芯片地址

并行总线的毗连:

1、数据总线、控造总线的毗连:

1)数据总线:

CPU:8条 P0口

拓展的芯片:一般也是8条,逐个对应毗连

2)控造总线:

CPU:读WR、写RD

可编程芯片:读、写信号逐个对应毗连,例如8255A的WR、RD

不成编程芯片:地址译码和读、写控造信号一路,例如74LS273的CLK,74LS244的2G

2、系统扩展的寻址办法-译码:

地址线的毗连是为扩展的芯片确定一个独一的地址,即存储器的地址空间范畴和I/O接口的端口地址

要扩展的芯片的地址线数目老是少于单片机地址总线的数目,如许就将51单片机的地址总线分为两部门:用到的地址线、没有用到的地址线

用到的地址线分为:高位地址线、低位地址线

1)线译码(未用的线设置位1)

线译码是操纵单片机的一根空闲高位地址线(凡是接纳P2的某根口线)选中一个外部扩展I/O端口芯片

Eg:以8255A为例:

CS设置为低电平,译码器的A0、A1口为输入端口

2)译码器译码

CPU的“低位地址线”用做I/O接口芯片的片内译码,“高位地址线”通过译码器芯片停止译码构成I/O接口芯片的片选

Eg:以74LS138为例,3-8译码器

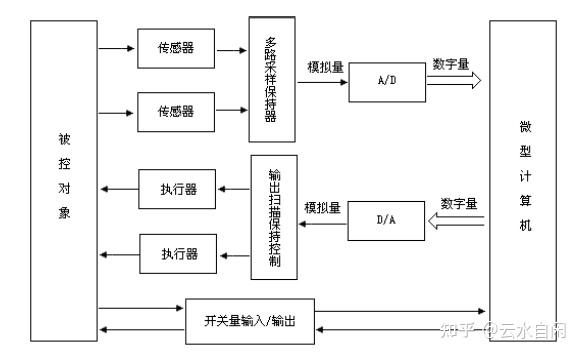

2、逐次比力式AD转换的原理

3、操纵DAC0832实现单缓冲和双缓冲的D/A转换输出

数模转换器:我们在设想时将D/A转换器设想成CPU的一个输出口,操做时向该口地址写入响应的数字量就能够了

分辩率:对模仿输出的最小分辩才能。设DAC位宽为n,则:

分辩率Δ=满量程电压/2n =Vref/2n

凡是分辩率也用输入数字量的位数来暗示。例如8位DA转换器,其分辩率为8位,12位DA转换器,其分辩率为12位1)单缓冲:输入存放器或DAC存放器中的肆意一个工做在曲通形态,而另一个工做在受控锁存形态。在只要单路模仿输出或虽有多路模仿输出但不要求同时刷新模仿输出时,可接纳那种体例

2)双缓冲:CPU对0832停止两步写操做:先将数据写入输入存放器再将输入存放器的内容写入DAC存放器

4、操纵ADC0809实现1路和多路的A/D转换输出

模数转换器:

51单片机读取ADC0809的转换数据可接纳:

无前提体例(延时)、查询体例、中断体例

1路:P2.7,即A15,则0809口地址为78FFH(IN0做为外部输入时)

多路: