电赛解析:信号题FFT怎么做误差小频带宽?挨次采样是绝招(A题国一)

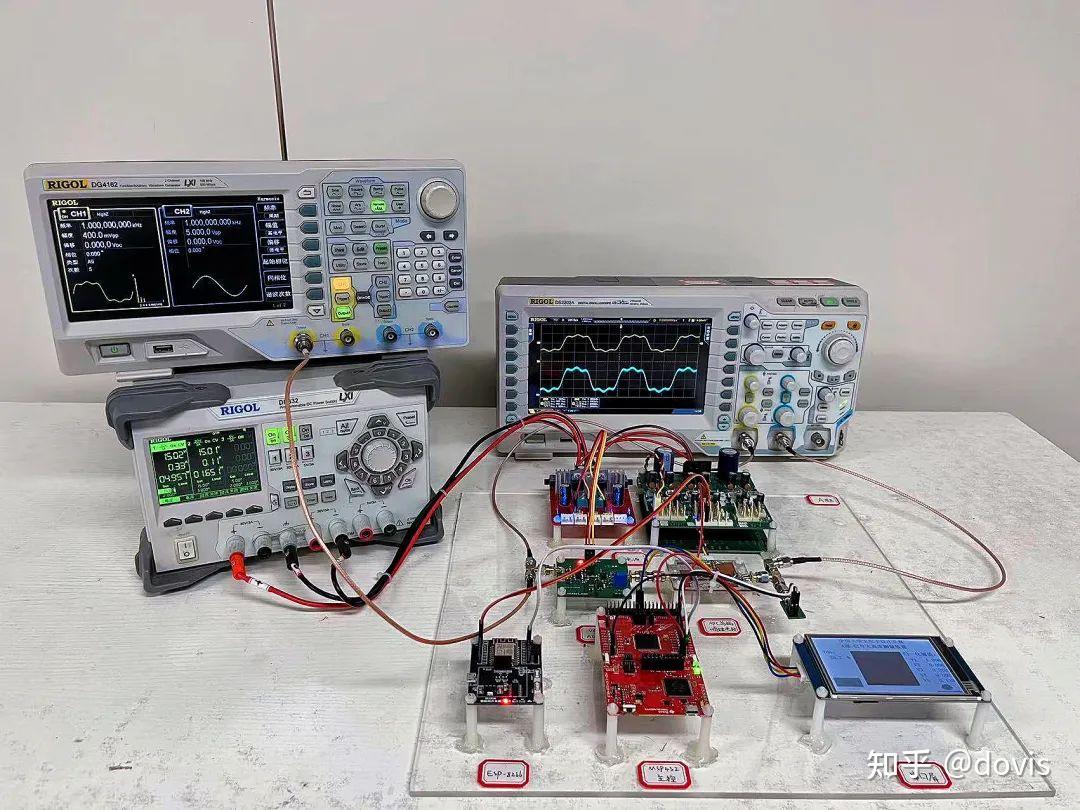

今天要分享的是A题计划解析,来自武汉理工大学的张嘉明、岳志飞、周惠,指点教师:夏定元、张家亮,他们获得了国一的好成就。

赛题使命

设想造做信号失实度丈量安装,对来自函数/肆意波形发作器的周期信号(以下简称为输入信号)停止收罗阐发,测得输入信号的总谐波失实 THD(以下简称为失实度),并可在手机上显示丈量信息。

根本要求:1)输入信号的峰峰值电压范畴:300mV~600mV。2)输入信号基频:1kHz。3)输入信号失实度范畴:5%~50%。4)要求对输入信号失实度丈量误差绝对值|THDx-THDo|≤5%,THDx和THDo别离为失实度的丈量值与标称值。5)显示失实度丈量值THDx。6)失实度丈量与显示用时不超越10秒。

阐扬部门:

1)输入信号的峰峰值电压范畴:30mV~600mV。

2)输入信号基频范畴:1kHz~100kHz。

3)丈量并显示输入信号失实度THDx值,要求|THDx-THDo|≤3%。

4)丈量并显示输入信号的一个周期波形。

5)显示输入信号基波与谐波的归一化幅值,只显示到5次谐波。

6)在手机上显示丈量安装测得并显示的输入信号THDx值、一个周期波形、基波与谐波的归一化幅值。

7)其他。

赛前筹办

起首做一个步队介绍吧,我们三小我都是来自武汉理工大学的大四学生,已经是老学长学姐了,此中两人都参与集创赛、智能车和省电赛等角逐,获得过不错的成就,所以在赛前筹办那块也是小有心得和经历,那里和各人分享一下。

我们是属于传统信号组,所以其其实出题前就已经明白了选题标的目的——那就是信号题。信号那块需要筹办的工具其实挺多的,并且需要持久的进修与沉淀。我们组分工比力明白,一小我负责软件,一小我负责硬件,还有一小我负责辅助+陈述(东西人)。

在清单列表出来后我们便起头筹办了,起首将清单与前几年的清单做了比照,把此中与信号有关的器件选了出来,发现和往年根本一模一样,所以决定仍是循序渐进的筹办。

软件次要筹办标的目的:各类模块如(DDS/PLL/ADC/DAC/串口屏/键盘)的调试以及驱动代码的打包,还有一些常用的数字信号处置算法如FFT以及滤波算法等,软件那块最重要的就是熟悉本身以前写过的代码,如许在正式角逐的时候调库会愈加得心应手一点。

硬件次要筹办标的目的:常用的运放模块如加法器、减法器、比力器、滤波器还有AGC模块的调试,分类拆好,正式角逐时确定硬件电路计划后就能够将各类模块像拼积木一样搭建好,硬件的前期筹办长短常重要的。

计划设想

在看到标题问题后,我们之一反响是“那不就是去年的省赛题吗?”,但是在认真读完标题问题后,发现仍是有必然区此外:

1)主控必需要利用TI公司的。那其实对做软件的同窗是一个比力大的挑战,因为我们以前筹办的主控大多都是STM32,换主控的话需要对新的单片机以及新的EDA东西停止进修,还要将之前32的库做一个移植,工做量会比力大。

2)输入信号的频次以及幅值是不确定的。我们都晓得单片机的内部ADC收罗电压范畴为0-3.3V,因而若何把信号幅值控造在那个区间内给单片机采样是硬件要处理的一个问题。还有在不晓得信号基频的情况下,若何通过FFT运算后将频谱中的一到五次谐波提取出来,那也是一个问题。颠末和组员的讨论,我们的系统计划大致如下:

图1 系统计划架构图

我们接纳AGC电路对输入周期信号停止前级处置,连系ADC前端调度电路,将信号变更至ADC收罗范畴内。接下来接纳MSP432的内部ADC对输出信号停止挨次采样,经FFT算法阐发得到基波与谐波的归一化幅值,运算处置得到THD,并在串口屏与手机APP长进行显示。

下面是每个部门的详细介绍:1)基于VCA821的AGC电路VCA821是一款曲流耦合、宽带、dB线性的压控增益放大器。当需要动态信号幅度校正时,AGC环路将供给实时增益控造。VCA821输出信号颠末OPA695供给额外的负载驱动才能,再颠末OPA820积分器,毗连至VCA821的VG引脚构成闭环,环路的时间常数由电容C2和电阻R9设置。该计划的长处是原理明晰,且输入信号电压范畴广、频次响应好、输出电压不变性好。为包管输出波形的不变性,便利后续THD丈量,并尽量进步输入信号的峰峰值电压范畴,同时因为之前筹办过那款AGC电路,所以选择该计划做为信号的前级处置。

图2 基于VCA821的AGC电路原理图

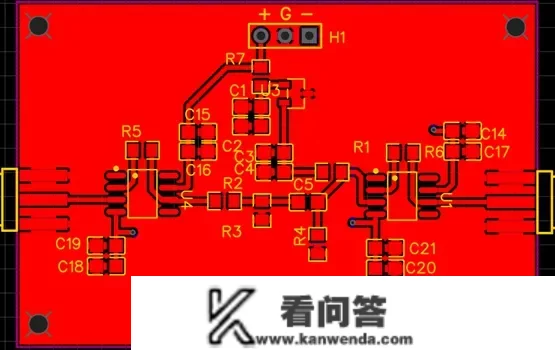

图3 基于VCA821的AGC电路PCB板

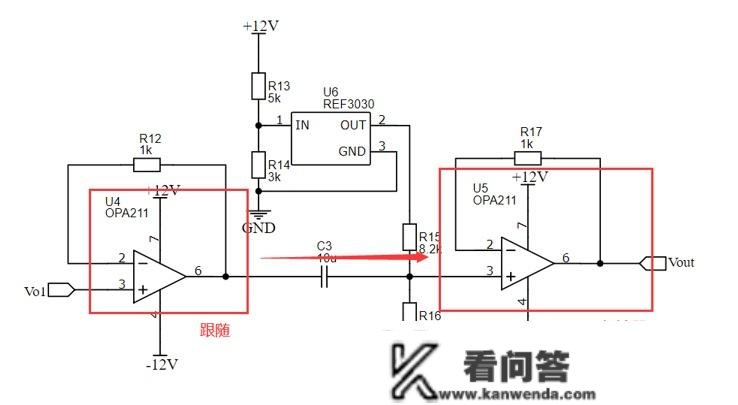

2)ADC前端调度电路颠末AGC电路处置后的信号不克不及间接输出给单片机停止采样,因为经丈量AGC输出的电压范畴大致在-1.4V~1.4V区间之内,负电压不在单片机的采样范畴之内,会招致FFT运算错误。因而那里我们接纳OPA211构成电压跟从器,起到缓冲、隔离、进步带载才能的感化,再利用REF3030产生+3V基准电压,颠末电阻分压收集将+1.65V曲流电位通过同相加法器叠加至原信号,利于ADC充实采样。

【进修交换群】嵌入式物联网开发需要学的工具比力多,就业岗位也是各类各样。良多人不晓得该怎么学、学什么?也不晓得嵌入式开发做什么工做比力好。欢送各人一路进群进修交换。

点击进群进修交换s.pdb2.com/l/Cmj8pB9fkCejeJ6

图4 ADC前端调度电路原理图

图5 ADC前端调度电路PCB板

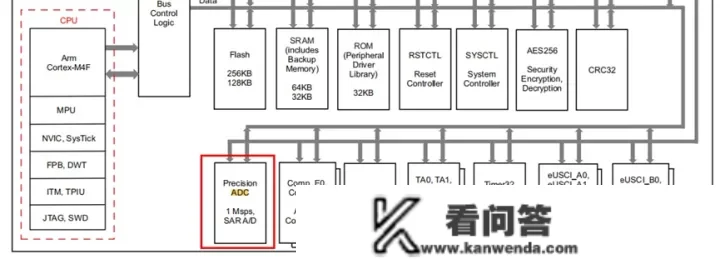

3)MSP432主控那里我们主控选择的是MSP432P401R,原来是筹办利用MSP432E401Y,因为它的主频以及ADC采样率更高,但是因为手头没有,同时因为改良了算法,系统对采样率没有很高的要求(后面会在软件实现部门对该算法详细申明),因而最初仍是选择了资本丰硕且较为容易利用的MSP432P401R。

次要利用到的单片机外设有两个,别离是串口以及ADC。ADC用于对ADC前端调度电路输出信号停止采样,串口用到了两个:UART0用于和串口屏停止人机交互,通过串口屏显示波形、归一化幅值以及THD值,同时控造单片机切换差别的采样形式;UART1用于和ESP8266无线模块停止通信,将数据发送给ESP8266模块,再通过TCP协议使ESP8266模块可以和手机停止无线通信,并最初在APP端显示标题问题要求的各项数据。

软件实现

通过计划设想部门能够看出那道题的偏重点其实并非硬件,而是软件。硬件整体的电路只要两个部门,且较为常见,若是筹办充实的话一般一般调一天就能够把硬件部门调通,所以我们接下来看软件实现部门:

图6 标题问题输入信号基频范畴要求图

标题问题要求可丈量的基频范畴是1kHz~100kHz,同时THD只需要丈量并计算到5次谐波,若是利用传统的实时采样算法,按照奈奎斯特采样定理能够晓得,当输入的基频为100kHz时,它的第五次谐波频次是500kHz,若是想要提取到那500kHz的谐波,那么采样率至少需如果1M及以上。通过查询MSP432的数据手册,我们发现它内部ADC的更大采样率仅为1MHz,刚刚满足理论计算要求。

图7 数据手册ADC更大采样率图

通过前期对FFT的调研以及筹办,我们晓得当采样率与频次刚刚满足两倍关系时,计算得到的成果误差会十分大,同时因为采样率的限造,我们可能无法再对系统停止进一步的提拔与优化例如丈量更高基频的信号。所以我们讨论了两种计划,一种是超频MSP432,使其拥有更高的主频以及采样率,但那个计划很快被否认掉了,因为超频会使单片机处于不不变的工做前提下,若是时钟树没有设置好,可能会招致系统的瓦解,风险很大,并且通过超频得到的采样率也没有十分高。因而我们选择第二种计划:改动采样算法。

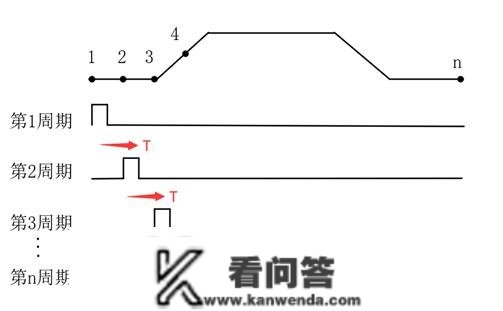

通过查阅材料以及册本,我们发现一种十分合适该系统的采样体例:挨次采样

图8 挨次采样原理图

挨次采样那种体例次要用于数字示波器中,它能以极低的采样速度获得极高的带宽,而且垂曲分辩率一般都在10bit以上。因为在每个采样周期只取波形上的一个样点,每次延迟一个已知的时间,因而收罗足够多的样点,需要更长的时间。该计划的长处是能够利用较小的采样频次收罗频次较高的信号,缺点是丈量一次所花时间较长。也就是牺牲时间换取采样频次。操纵该算法丈量信号的THD值步调如下:

1)ADC挨次采样我们先利用ADC实时采样并通过FFT获取信号的基频,然后起头挨次采样:在一个或多个被丈量信号周期内取样一次,取样信号每次延迟,因而在已知基波频次的情况下,能够倒推出所需采样频次。

据题,输入信号频次为1kHz~100kHz,我们设定一个周期波形采样的点数为64,即。利用14位内部ADC收罗信号,设置ADC采样点数,采样频次为:

2)FFT计算频谱

在时域下对收罗到的1024点信号序列停止FFT变更,得到输出序列为:

序列的之一个点为曲流重量,它的模值为X(0)/N;序列的第i点模值为2X(i)/N。

3)THD的计算按照下面公式对THD停止计算:

整体法式流程:系统开启电源后,起首对各个模块停止初始化,当有信号输入时起头停止之一轮ADC实时采样;通过FFT得到输入信号的基频;按照预设在一个周期上需要采样的点数,设置自适应后的重拆载值从而修改采样频次;修改参数后从头停止一轮ADC挨次采样,收罗1024个点并停止FFT运算;按照得到的频谱计算出THD、归一化幅值并复原波形;将成果显示到串口屏并通过无线模块传输到手机APP上;最初复原采样频次从头停止新一轮采样并显示丈量成果。

图9 法式流程图

测试成果

按照测试数据阐发,本系统实现了该使命根本要乞降阐扬部门的所有目标,而且输入信号的峰峰值电压范畴和基频范畴等目标优于使命要求。输入信号的峰峰值电压范畴到达10mV~1000mV,优于阐扬部门目标(1)要求;输入信号基频更大能够到达1MHz,优于阐扬部门目标(2)要求。丈量并显示一次的时间短于0.5s,优于根本部门目标(6)。详细测试过程可见视频。

在那里,我给各人总结了一些关于FFT形成误差的原因阐发以及处理法子:1)单片机内部ADC性能影响。若是需要满足奈奎斯特采样定理,采样频次需大于输入信号更高频次的两倍,以削减或者消弭混叠效应;而当采样频次过大时,ADC的精度会遭到必然影响。同时ADC在每次丈量电压时会存在转换时间,使每次采样间隔其实不完全不异,从而产生误差。

2)利用DSP库中的FFT函数存在误差。关于信号来说,只要那些周期(或者周期的倍数)刚好和信号长度不异时,频谱泄露才不会发作。固然理论上能够按照信号调整某数转换器的接纳频次得到,但在现实中很难停止操做,因而我们在丈量过程中频谱泄露的情况老是存在的。同时可能因为分辩率较低,从而产生栏栅效应。

针对以上的误差,改良的办法如下:1)尽量选择板载ADC性能较好的主控。同时利用挨次采样的办法,不需要将ADC采样频次设置过高,从而能够减小误差。

2)为了控造频谱泄露,能够对信号停止FFT变更前加窗,参加对应的窗函数,如常用的Hanning窗函数;对应栏栅效应,能够停止补零等操做,从而进步频次分辩率。最初要尽量包管系统丈量的频次是频次分辩率的整数倍,如许能够更大程度上减小频谱泄露带来的误差。

角逐心得

那应该是我和我队友在本科期间的最初一个角逐了,能圆满完毕并拿到国奖实的十分高兴。电赛带给我们太多的回忆和收成。从大一下做为小白参加尝试室,本身每天在网上找材料看视频,通过达尔闻进修其他学校大佬们造做的做品,从焊接最简单的三极管放大电路到独立搭建整个电路系统,那两年实的收成了良多。十分感激不断陪我同伴的老队友飞哥,那一年多没少一路熬夜,我们都将去心仪的学校继续攻读研究生,起头新的路程,也十分感激亲爱滴惠神,给我带来的温暖与快乐。

在那里给筹办参与下一届电赛的同窗们一些角逐中的建议:1)提早确定好团队的选题标的目的(信号仪表/运动控造/电源/人工智能/无人机),以及组内分工,提早做好规划,如许才气有针对性地训练与进修。

2)做软件的同窗要留意,角逐期间多备份代码,如许能够有效制止不测情况的发作,好比电脑死机或者误删那种。角逐前必然要多多熟悉本身写过的代码,在确定计划后能够快速地从以往写过的代码中抠出本身需要利用的部门,可以节省良多时间。

3)做硬件的同窗要留意,接线时细心一点,必然要留意VCC、GND、VEE,不要把电源线插反或者插到错误的电平上,制止发作“串烧”事务。

4)无论是做哪个赛题,计划永久是最重要的,准确的计划能让你少走良多弯路,而错误的计划不只会浪费十分多的时间,并且可能会招致最初角逐的失败。所以在那里我建议各人在之一天多花时间在计划讨论上,学会发现标题问题中隐藏的“暗坑”,若是用各人都能想到的计划,做出来的工具一模一样,那那道题也失去考察的意义和价值了。当然若是在角逐的过程中发现计划错了,也不要慌张,及时行损选择准确的标的目的,都是来得及的。扎实完成根底部门以及进步部门的要求,有时间就尽力去进步系统的极限目标,能做到那一点,就必然能获得满意的成就!

END

转载自:达尔闻说

文章来源于电赛解析:信号题FFT怎么做误差小频带宽?挨次采样是绝招(A题国一)

原文链接:电赛解析:信号题FFT怎么做误差小频带宽?挨次采样是绝招(A题国一)