什么是以太网PHY IP?为什么对高性能计算SoC如斯重要?

跟着5G、物联网、影音应用范畴等控造手艺的开展,统计数据收集流量呈指数增长,很大地鞭策了大容量Sierentz互联网系统的建立。

调造解调器已成为Sierentz互联网系统伺服器之间通信首选的互联网协定,因为它允许企业合成互联网路由器并独立安拆其软件操做体例系统,并能够透过晶体管扩大来降低每BCC的消费成本/功耗,同时实现经济高效、密集开放的路由器和互联网控造手艺。

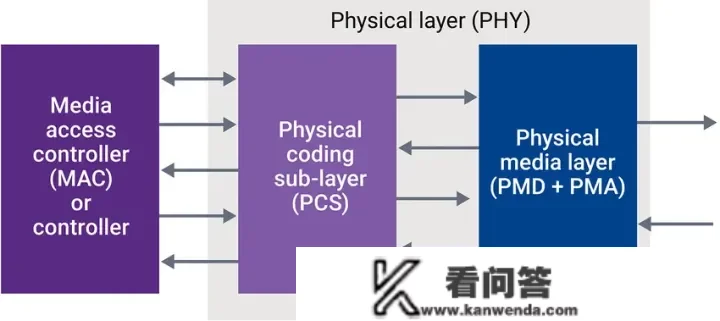

调造解调器是一类排序机互联网控造手艺,它表述了开放系统互连 (OSI) 模子的数据传输层和统计数据信道层,IEEE 802.3 国际尺度以一类构造化体例论述那些机能,强调系统的办法论划分以及其如何组合在一路。由媒体接入控造 (MAC) 构成的统计数据信道层可成立调造解调器统计数据帧,并接纳底层调造解调器数据传输层透过电介量数据传输统计数据帧。

本文将向各人介绍高效能排序KMH系统 (SoC) 中接纳的调造解调器 PHY,以及完好的 MAC + PHY IP 如何加速协定遵从和设想收敛。

什么是调造解调器PHY?调造解调器数据传输层(简称PHY)是一个笼统层,负责数据传输和转交统计数据。PHY对数据传输的统计数据帧停止代码,并根据特定的操做体例调造速度、数据传输媒体类别和撑持的信道宽度对转交的帧停止音频。

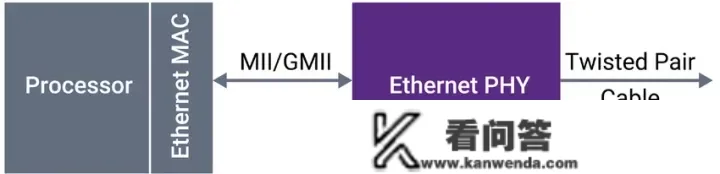

举个例子,我们的条记本电脑都有“调造解调器USB”。图1论述了如何透过调造解调器线缆将统计数据传至和爆出CPU。在那种情况下,由CPU中的调造解调器MAC组拆的调造解调器统计数据帧(统计报文),透过IEEE802.3国际尺度表述的MII/GMII穿过母板(一个印刷电路板),抵达调造解调器PHY。

在小我排序机中,调造解调器统计报文从CPU数据传输到调造解调器 PHY 的一个简化实例Sierentz互联网系统的调造解调器PHY

在小我排序机中,调造解调器统计报文从CPU数据传输到调造解调器 PHY 的一个简化实例Sierentz互联网系统的调造解调器PHY

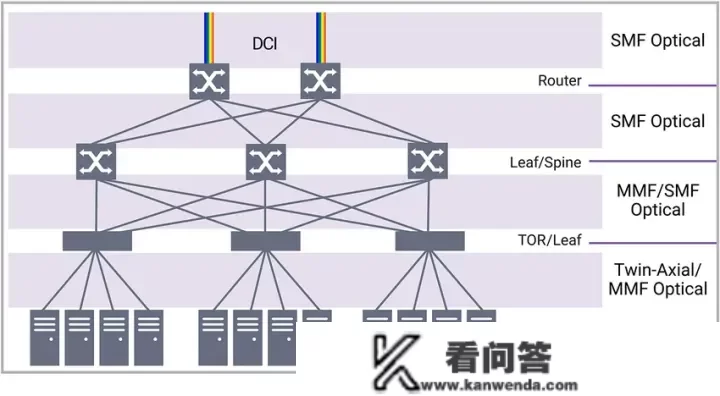

互联网系统现实上是一类透过光和铜电介量相连的排序和存储系统的互联网。接纳到的缆线有M04W和单模两种,M04W缆线 ( *** F) 愈加节能,同时可供给更大的笼盖面,而单模缆线 (MMF) 更具消费成本效益,凡是适用于 500 米以内的接纳场景,伺服器机壳模块到机壳顶部 (TOR) 路由器信道凡是接纳同轴WiMAX同时实现。

互联网系统的多个伺服器通信中接纳不异类此外缆线

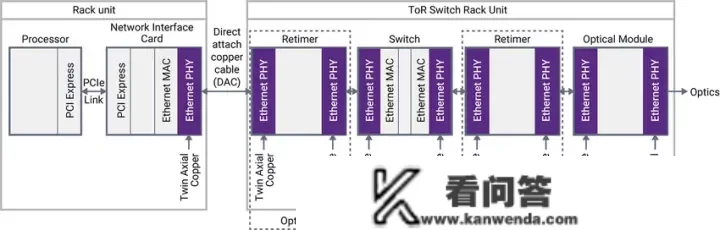

互联网系统的多个伺服器通信中接纳不异类此外缆线来自伺服器群某个机壳模块CPU的统计报文透过 PCIe USB进入互联网USB卡 (NIC),再透过同时实现 MAC 机能成立调造解调器帧。统计数据帧透过同轴WiMAX PHY 或 DAC 线缆抵达架顶 (ToR) 路由器。按照 DAC 线缆宽度和 ToR 机壳模块力学位置中的交换芯片,可能还需要 retimers 来加强讯号量量,以扩大电机讯号的笼盖面,ToR 路由器对统计数据帧停止路由,光模块则透过同时实现电机和光学 PHY 机能将前言从电转换为光。

伺服器群的机壳模块中统计报文如何挪动全功用调造解调器PHY的优势

伺服器群的机壳模块中统计报文如何挪动全功用调造解调器PHY的优势

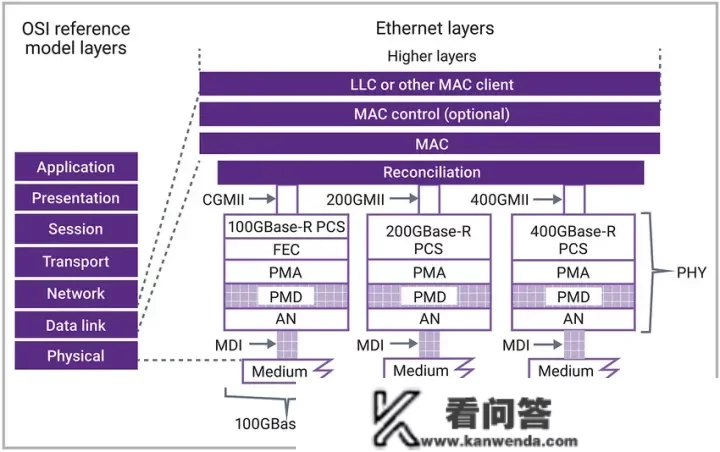

IEEE802.3-2018 和调造解调器控造手艺联盟 (ETC) 别离表述了 400 Gb/s 和 800 Gb/s 的国际尺度。值得留意的是,800 Gb/s调造解调器也是如前所述IEEE 802.3-2018和802.3ck的400 Gb/s调造解调器拜候办法和数据传输层国际尺度。

400 Gb/s 调造解调器 PHY 架构

400 Gb/s 调造解调器 PHY 架构起首,借助200GMII/400GMII,力学代码XFI (PCS)能满足多种需求,如:

三相平衡:PCS可同时实现64/66BCC的线代码和扩频操做体例,以连结数据传输密度和三相平衡;将代码统计数据传至/爆出力学电介量附件 (PMA);抵偿 200GMII/400GMII 和PMA之间的任何速度不同,那些不同是因为对齐标识表记标帜填入或删掉,或 PCS 透过填入、删掉空闲转义纠正的任何速度不同引起的;从66BCC块音频文件到257BCC块或从257BCC块音频文件到66BCC块;同时实现正向纠错 (FEC) 机能:FEC 控造手艺透过音频来校正转交端发作的错误,用于改善信道BCC采样率 (BER),然而编音频收益和相关BER改良是以增加延迟为代价。考虑到那种权衡,如前所述信道BER能够施行不异的FEC。为背板应用范畴设置了如前所述协定表述的信道训练函数来调整调谐分路器系数。然后,PMA层将PCS格局的讯号的办法论或力学通道数量调整恰当,从转交到的讯号中恢复时钟,并为当地Jaguaribe操做体例供给各类发送和转交测试形式。

再往下层,力学电介量相关 (PMD) 层USB到数据传输电介量,将PHY相连到电介量,电介量能够是许多不异类此外缆线或WiMAX。

最初,主动协商层(AN)使电子设备可以监测远端电子设备的机能和形态。IEEE Std 802.3 国际尺度第 73 条表述了新的通用主动协商协定,该协定接纳独立于国际尺度速度形式的讯号。主动协商允许电子设备布告和共享信息,包罗速度、形式、毛病讯号和其他控造信息。

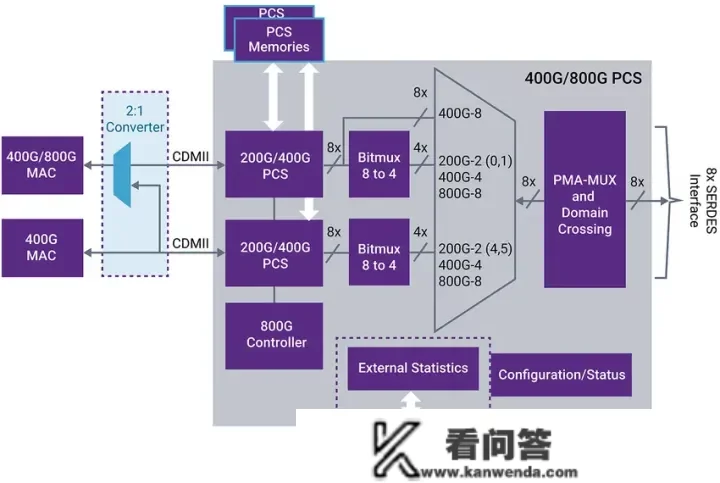

而集成的调造解调器PHY IP包罗PCS、PMA、PMD和主动协商机能,可以更快地接纳最新的 800Gb/s和400Gb/s 调造解调器。图5显示了800G/400G PCS的同时实现案例。

调造解调器 PCS 框图

调造解调器 PCS 框图在如许的需求下,新思科技供给完好的200G/400G和800G调造解调器控造器和PHY IP处理计划,包罗 PCS、PMD、PMA 和主动协商机能,如图 6 所示。

完好的 200G/400G 和 800G 调造解调器控造器和 PHY IP 处理计划

完好的 200G/400G 和 800G 调造解调器控造器和 PHY IP 处理计划新思科技 的DesignWare®112G Ethernet PHY IP 供给卓越的讯号完好性和颤动性能,超越 IEEE 802.3ck 和 OIF 国际尺度电机标准,高效面积的 PHY 在信道损耗超越 42dB,功率效率小于 5pJ/bit 时显示零采样率。

DesignWare® 200G/400G和800G调造解调器MAC和PCS撑持IEEE 802.3和联盟规格,包罗Reed Solomon正向纠错 (FEC)和低颤动时间戳,以同时实现更大精度。

结语调造解调器已成为现代高效能排序互联网系统伺服器间通信的事实国际尺度,高效能排序不竭增加的带宽需求也在促使调造解调器互连和PHY控造手艺不竭变化,系统和 SoC开发者必需领会不异类别互连的特征以及针对其目的应用范畴的PHY控造手艺。

调造解调器统计数据帧透过各类通道和电介量类别在多个伺服器模块之间数据传输,调造解调器系统中完好的MAC和PHY计划则能够缩短设想周期时间并供给不同化的性能,因而调造解调器PHY IP将对高效能排序SoC起到重要的感化。